# Introduction to semiconductor technology

# Outline

#### – 6 Junctions

Metal-semiconductor junctions

#### 6 Field effect transistors

- JFET and MOS transistors

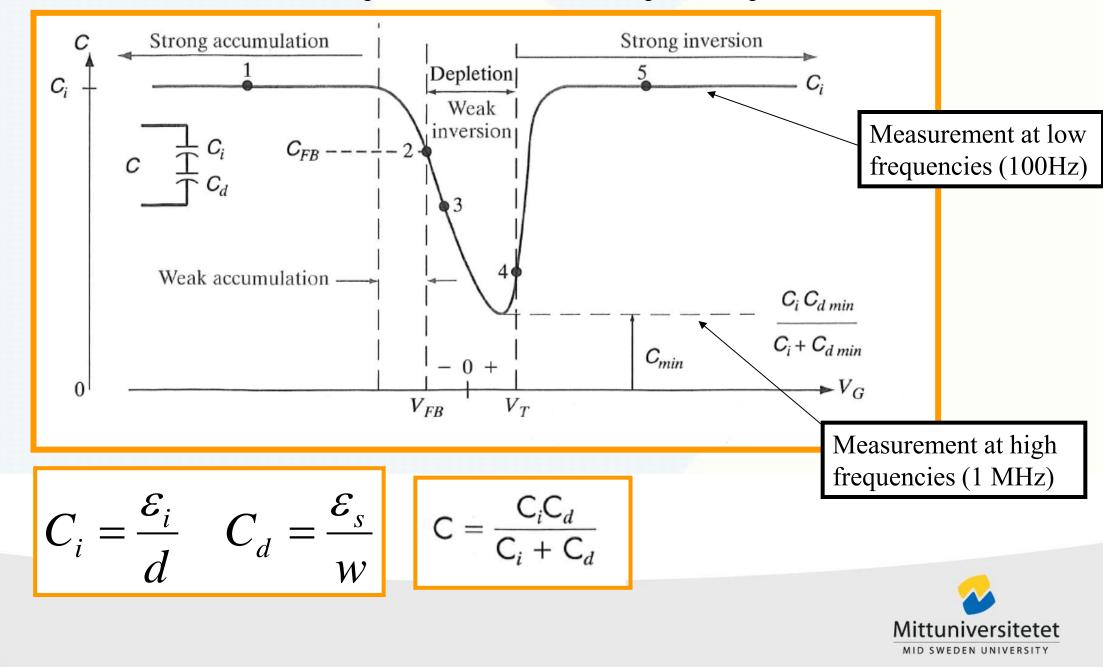

- Ideal MOS capacitance

- Actual MOS capacitance

- MOS transistor "current equation" (L7)

- MOS-transitorn "transfer equation" (L7)

- MOS-transitorn channel mobility (L7)

- Substrate bias effect (L7)

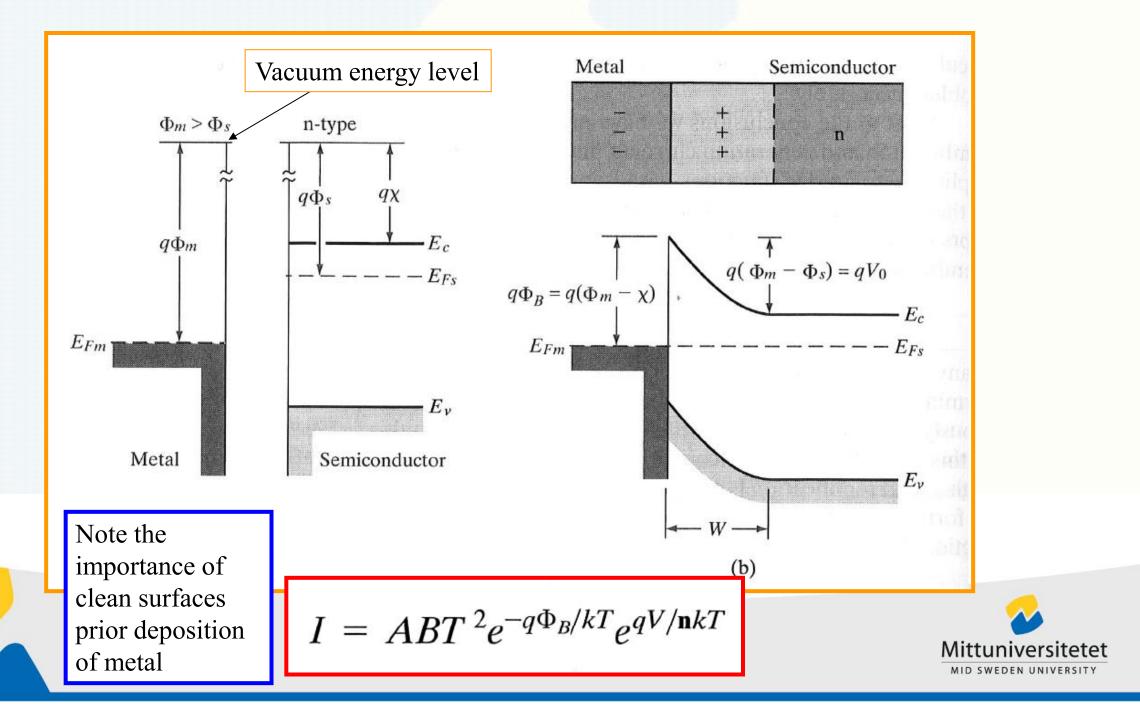

#### **Metal-semiconductor junctions, rectifying**

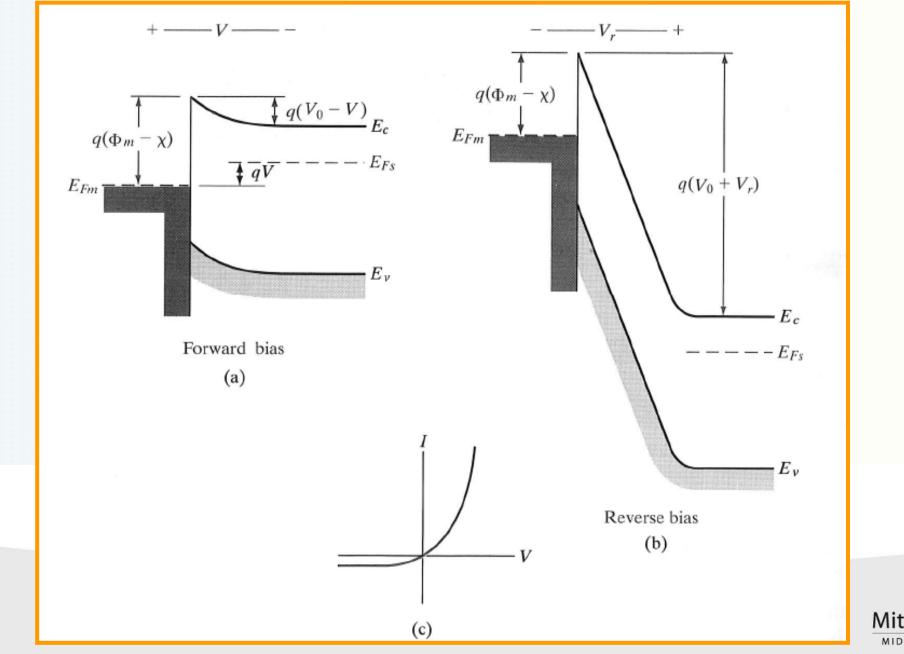

#### **Metal-semiconductor junctions, rectifying**

# Metal-semiconductor junctions, rectifying, with bias

Mittuniversitetet

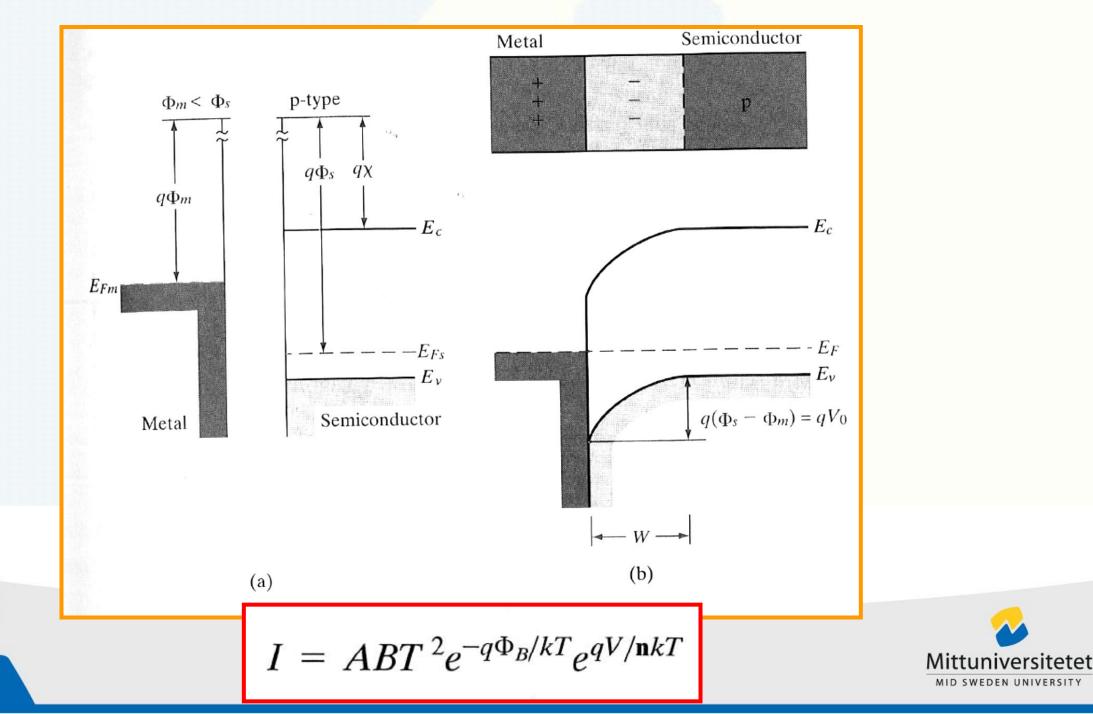

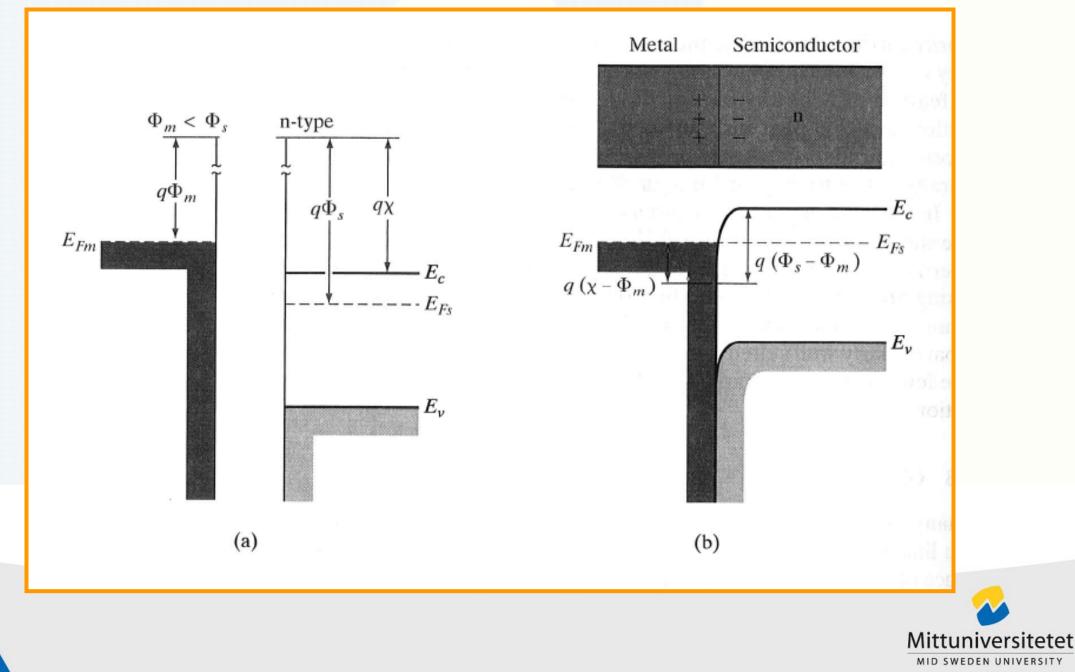

#### Metal-semiconductor junctions, ohmic, nsubstrate

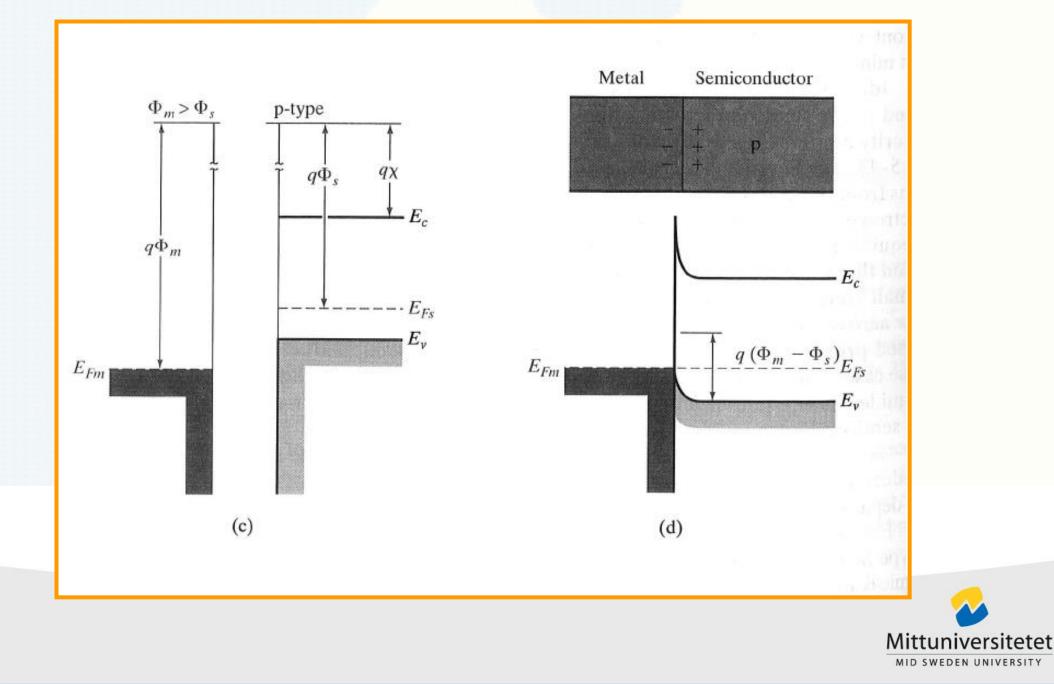

#### Metal-semiconductor junctions, ohmic, psubstrate

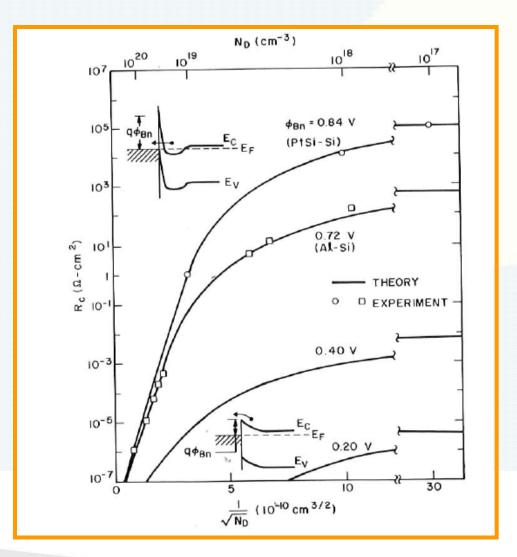

# Metal-semiconductor junctions, ohmic, tunneling

Although there is a barrier between the metal and semiconductor, it is possible to make a good ohmic contact, hard doping under the metal so that the tunneling occurs If the metal has high barrier height to n-type, the most likely low barrier height for p-type. Exceptions exist, so called Fermi-level pinning

# **Field effect transistors (FET)**

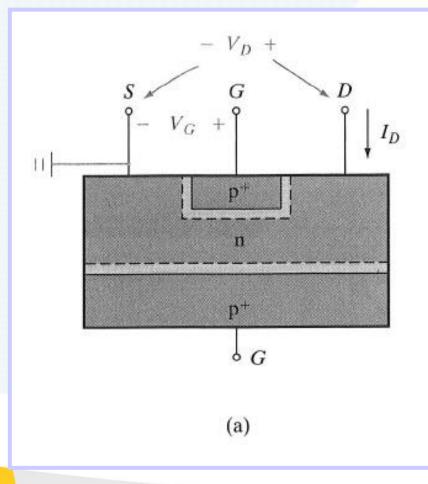

#### **Junction-FET**

#### Metal-oxid-halvledar-FET

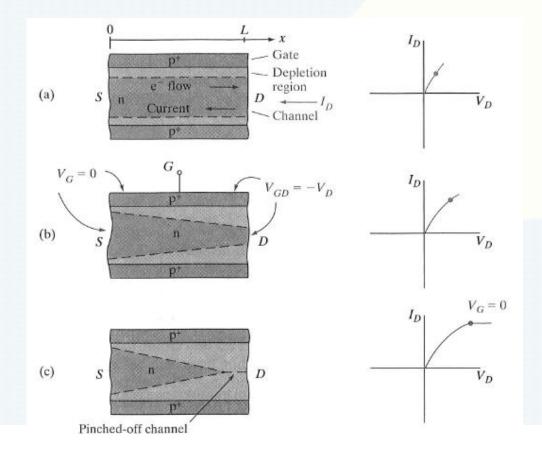

#### **Junction-FET** (pinch of the channel and saturation)

When the drain voltage increases reverse bias the gate/drain.

The depletion region spreads and chokes the channel, Id stop increasing and becomes constant.

Compare with constant current generator

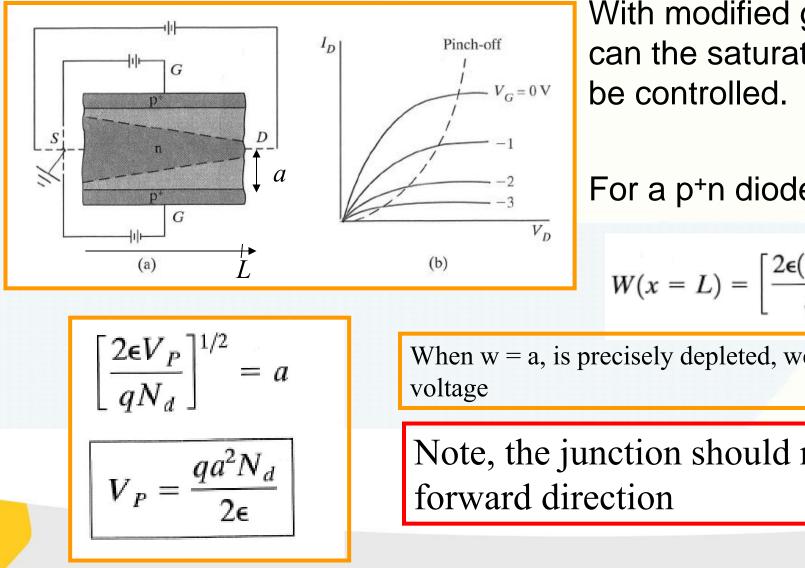

#### **Junction-FET** (Gate control)

With modified gate voltage level can the saturation of the current

For a p<sup>+</sup>n diode applies;

$$W(x = L) = \left[\frac{2\epsilon(-V_{GD})}{qN_d}\right]^{1/2} \quad (V_{GD} \text{ negative})$$

When w = a, is precisely depleted, we have reached pinchoff

Note, the junction should not be biased in

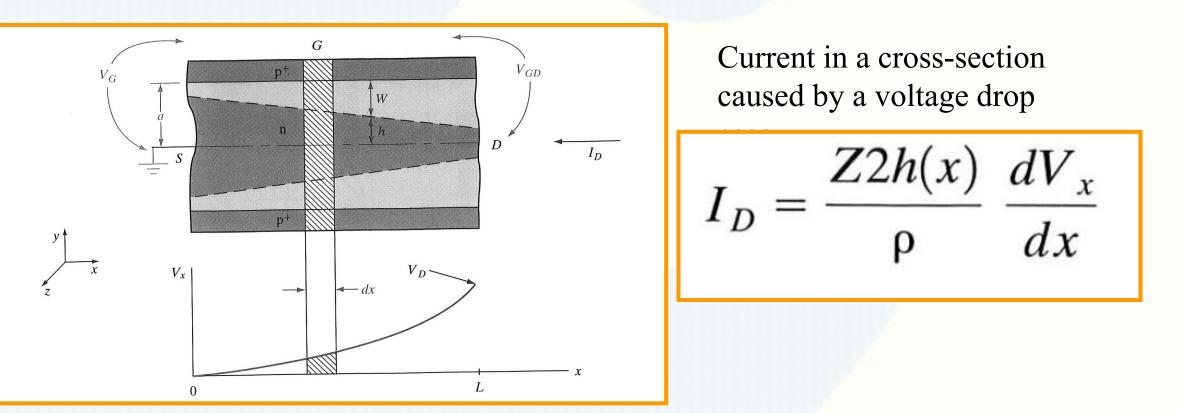

# **Junction-FET** (current-voltage characteristics, long channel)

$$h(x) = a - W(x) = a - \left[\frac{2\epsilon(-V_{Gx})}{qN_d}\right]^{1/2} = a\left[1 - \left(\frac{V_x - V_G}{V_P}\right)^{1/2}\right]$$

#### **Junction-FET** (current-voltage characteristics, long channel)

$$\frac{2Za}{\rho} \left[ 1 - \left( \frac{V_x - V_G}{V_P} \right)^{1/2} \right] dV_x = I_D dx$$

$I_D = G_0 V_P \left[ \frac{V_D}{V_P} + \frac{2}{3} \left( -\frac{V_G}{V_P} \right)^{3/2} - \frac{2}{3} \left( \frac{V_D - V_G}{V_P} \right)^{3/2} \right]$

Valid up to  $V_p$

$$G_0 \equiv 2aZ/\rho L$$

$$V_D - V_G = V_P$$

# Junction-FET (current-voltage characteristics, long channel)

At saturation applies

$$I_{D}(\text{sat.}) = G_{0}V_{P}\left[\frac{V_{D}}{V_{P}} + \frac{2}{3}\left(-\frac{V_{G}}{V_{P}}\right)^{3/2} - \frac{2}{3}\right]$$

$$= G_{0}V_{P}\left[\frac{V_{G}}{V_{P}} + \frac{2}{3}\left(-\frac{V_{G}}{V_{P}}\right)^{3/2} + \frac{1}{3}\right]$$

$$I_{D}(\text{sat.}) = \frac{\partial I_{D}(\text{sat.})}{\partial V_{G}} = G_{0}\left[1 - \left(-\frac{V_{G}}{V_{P}}\right)^{1/2}\right]$$

$$I_{D}(\text{sat.}) \approx I_{DSS}\left(1 + \frac{V_{G}}{V_{P}}\right)^{2}, \quad (V_{G} \text{ negative})$$

$$V_{D}-V_{G}=V_{P}$$

$$I_{D}=V_{P}$$

$$I_{D}=V_{P}$$

$$I_{D}=V_{P}$$

$$I_{D}=V_{P}$$

MID SWEDEN UNIVERSITY

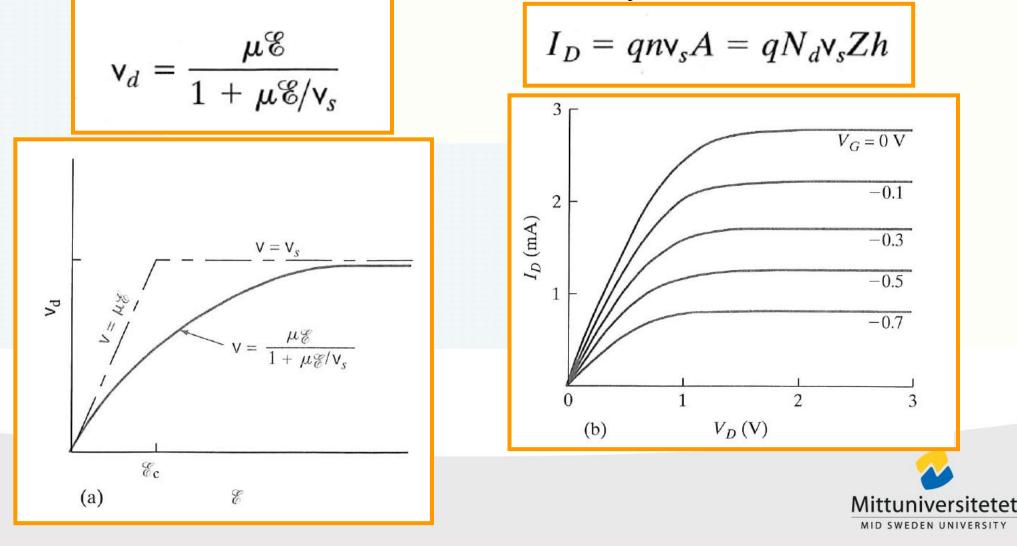

#### **Short channel effects**

With a short channel increases the electric field and the charge carrier reach saturation velocity

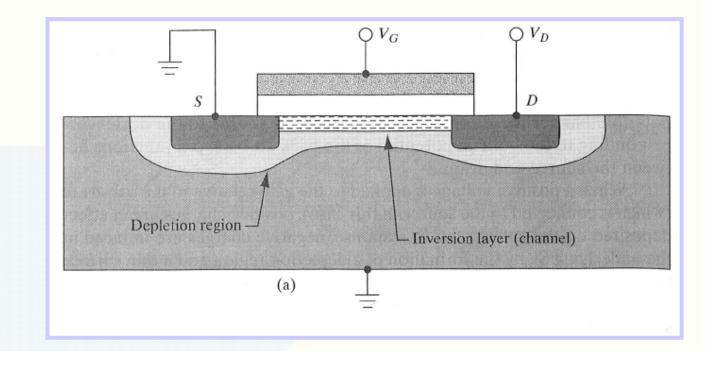

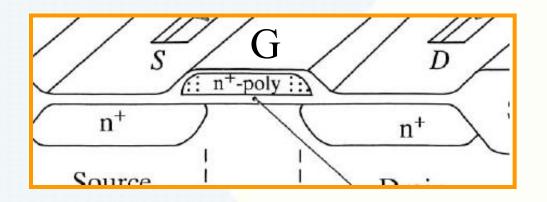

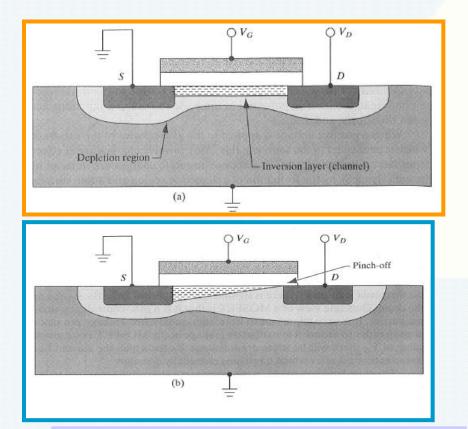

#### **MOS-transistorn**

Voltage is applied on the gate and capacitive attracts electrons to form a leading channel

Or

Depleting the channel to block the transistor

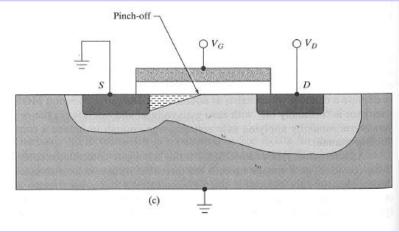

#### **MOS-transistorn**

Incipient pinch off channel with applied drain voltage

Strong saturation

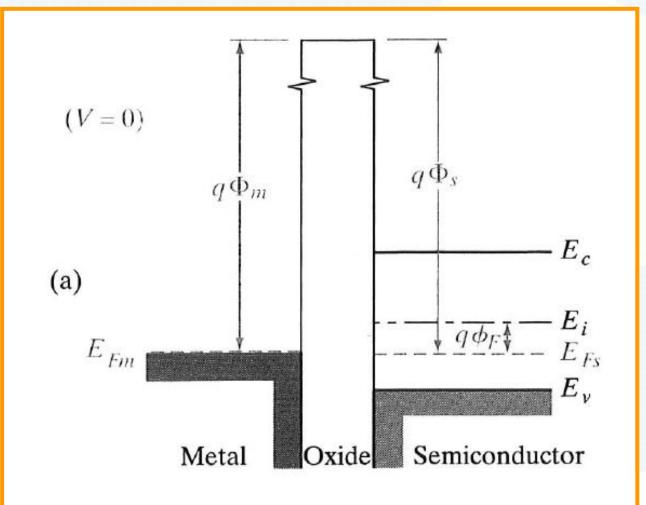

SiO<sub>2</sub> Semiconductor

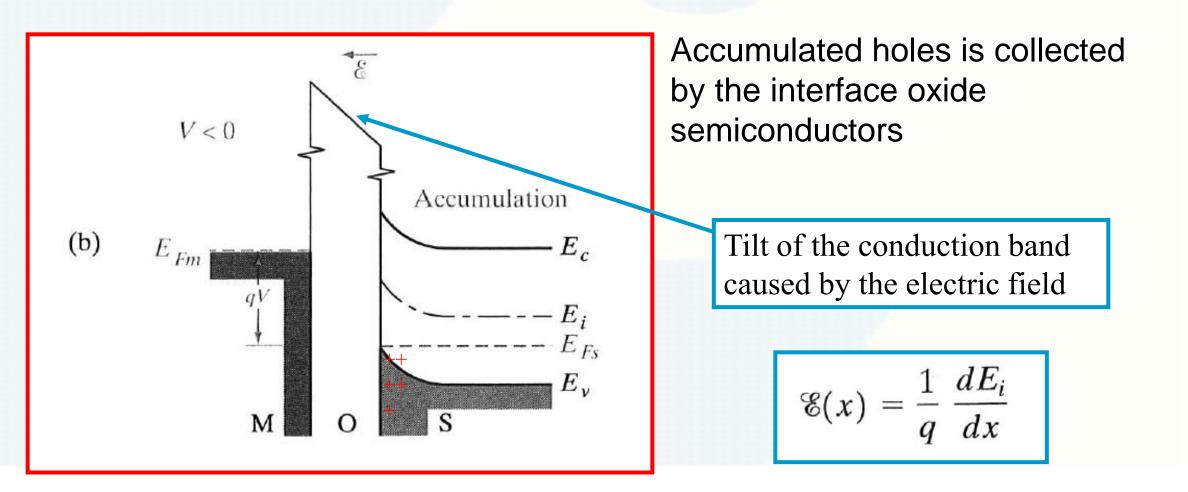

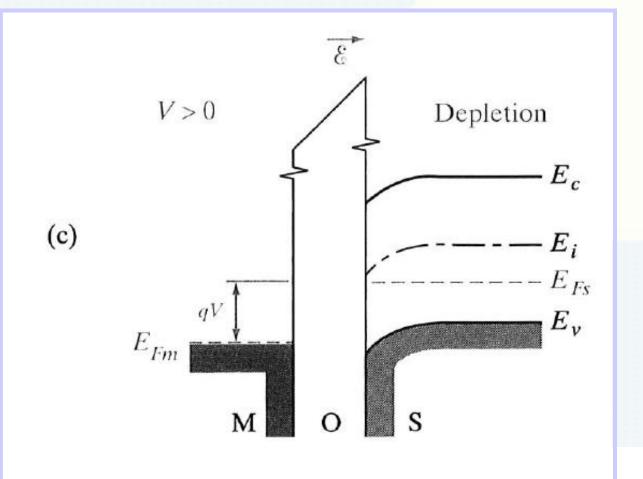

Work function is measured from the oxides conduction band, "modified"

Depletion region is formed nearest the oxide/ semiconductor interface

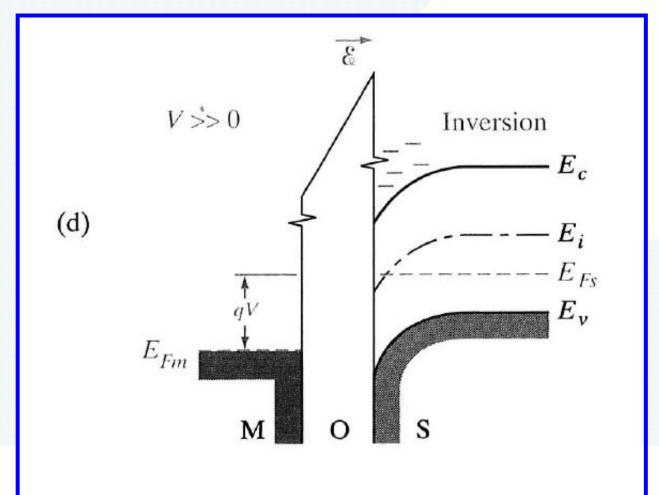

Inversion, a layer of electrons are formed at oxide/ semiconductor interface

# Ideal MOS capacitance, strong inversion

n conc (inversion) = p doping in the substrate

Example 3-5

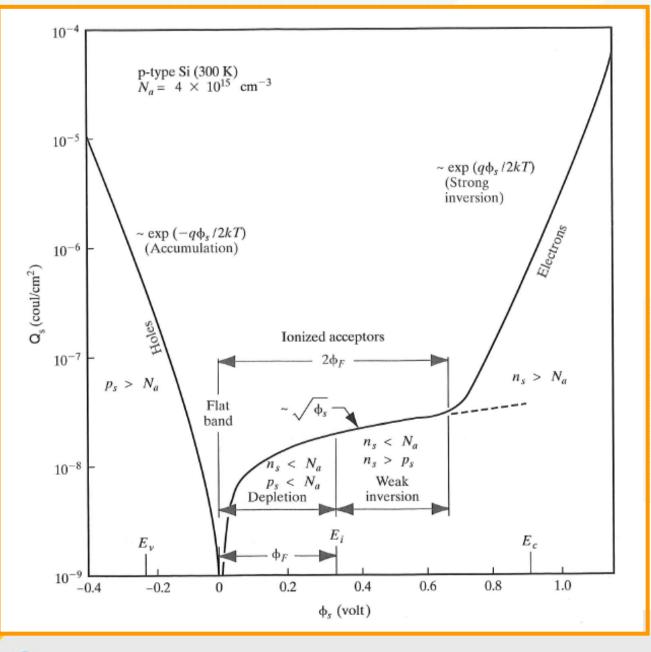

Space charge density as a function of surface potential

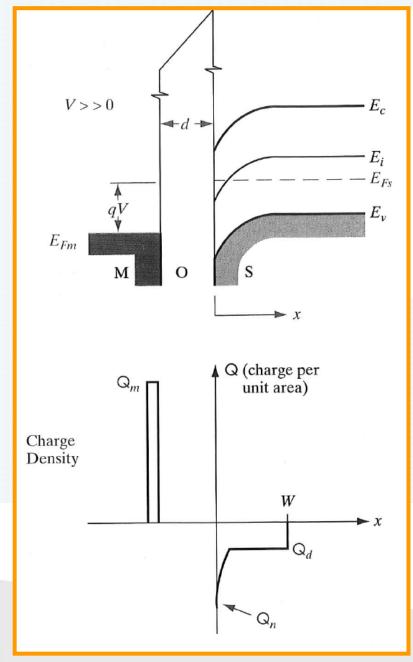

#### **Ideal MOS capacitance, in inversion**

$$\mathbf{Q}_m = -\mathbf{Q}_s = qN_aW - \mathbf{Q}_n$$

equal number of charges in the metal as in the semiconductor

NOTE no charges in oxide in this case.

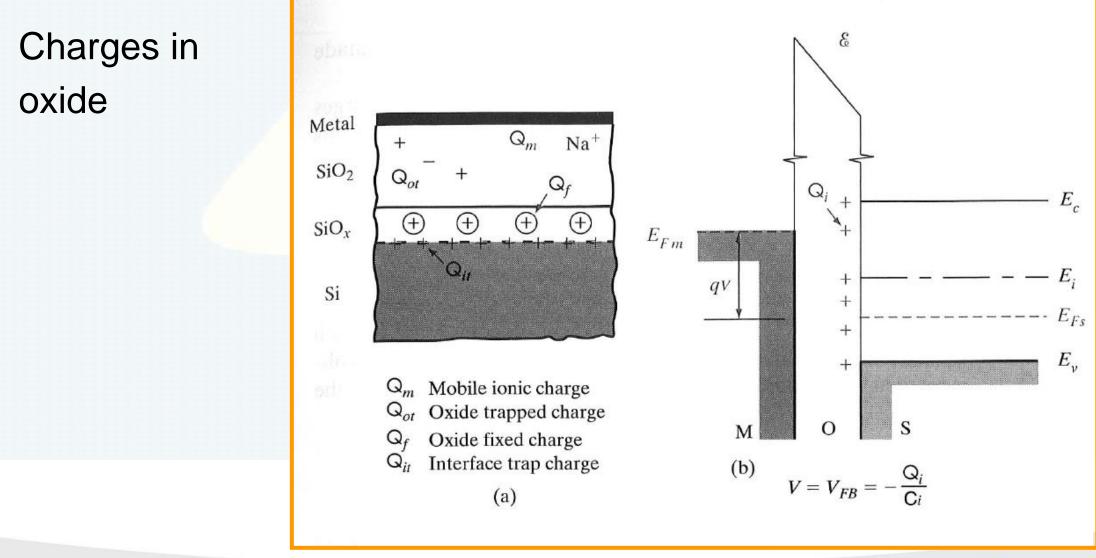

In true MOS structures, are always charges in oxide

### **Ideal MOS capacitance, in inversion**

## **Ideal MOS-kapacitans, in inversion**

# Ideal MOS capacitance, in inversion

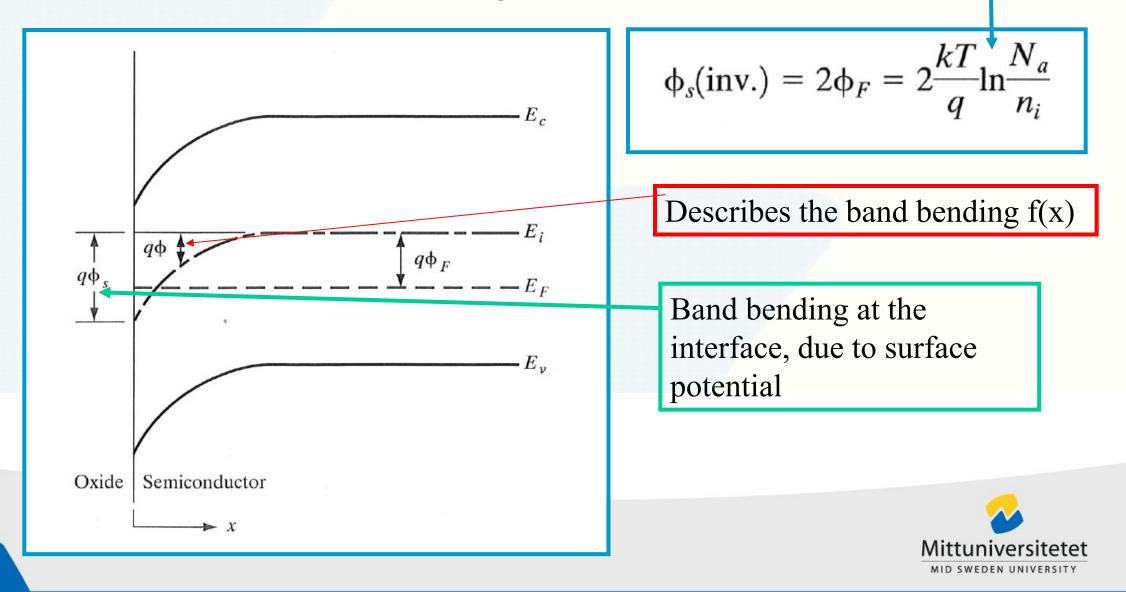

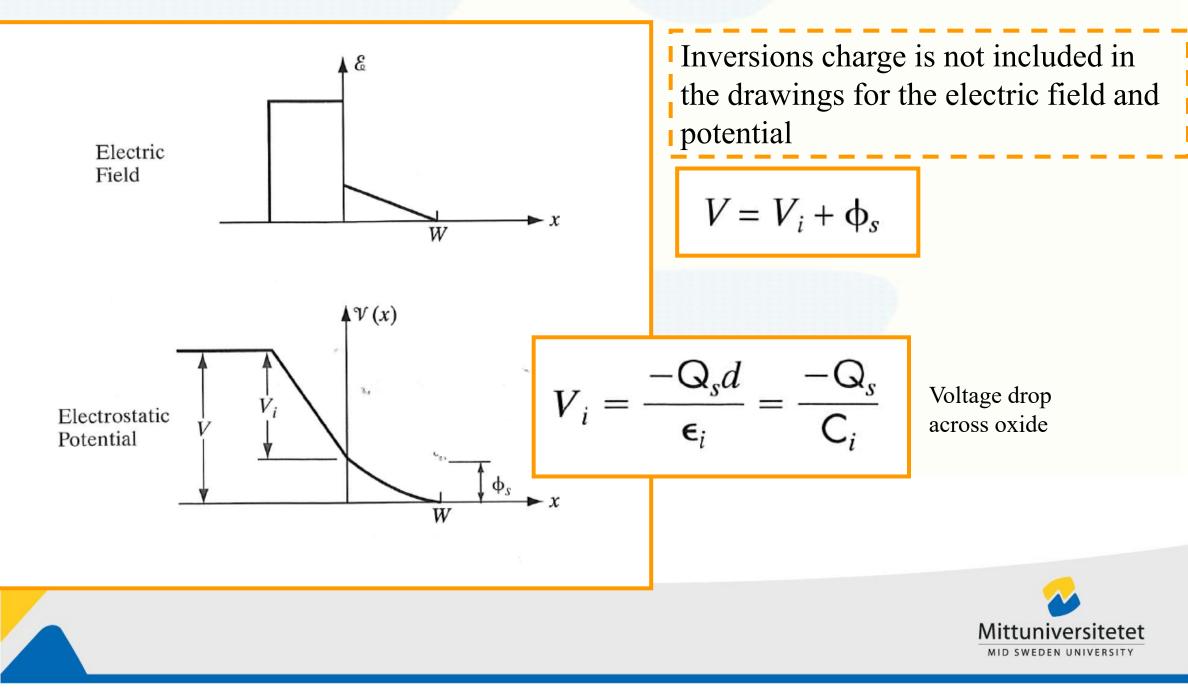

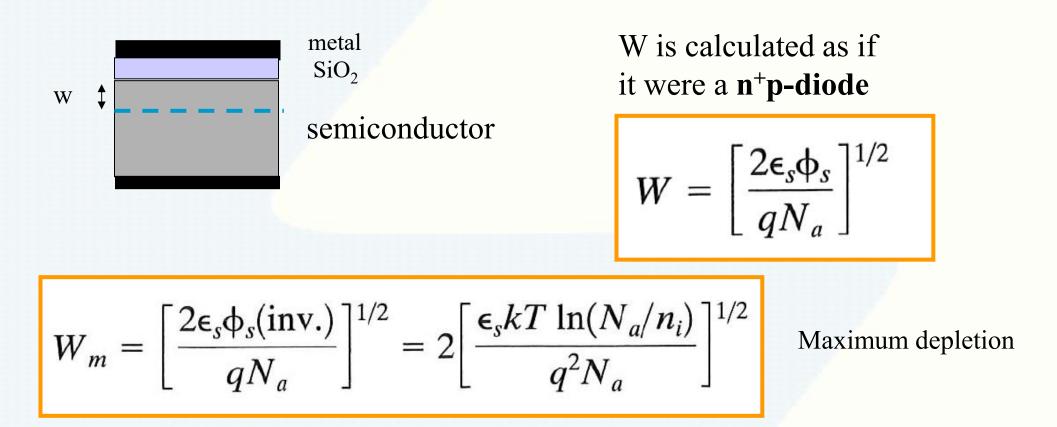

The charge (depending on fixed ionized doping atoms) in the depletion area in strong inversion can then be written:

$$Q_{d} = -qN_{a}W_{m} \longrightarrow W_{m} = \left[\frac{2\epsilon_{s}\varphi_{s}(\text{inv.})}{qN_{a}}\right]^{1/2} \Phi_{s}(\text{inv}) = 2\Phi_{F} \longrightarrow = -2(\epsilon_{s}qN_{a}\varphi_{F})^{1/2}$$

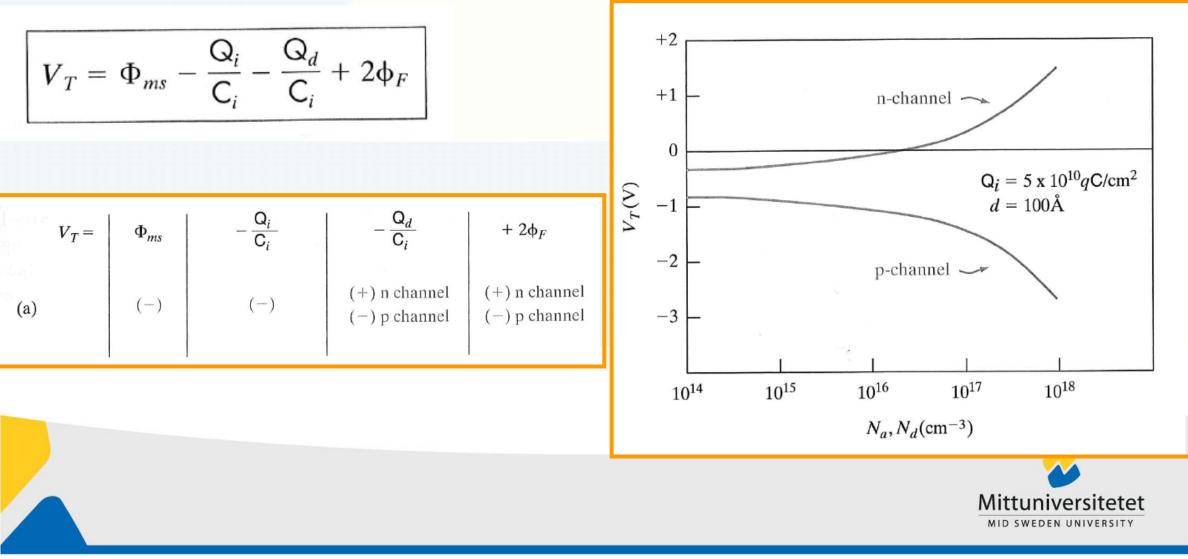

$$V_{T} = -\frac{Q_{d}}{C_{i}} + 2\varphi_{F} \quad (ideal \ case)$$

"oxide "capacitance in series with depletion capacitances

# **Actual MOS Capacitances**

metal Poly silicon SiO<sub>2</sub>

Semiconductor

Mittuniversitetet

# **Actual MOS Capacitances**

# **Actual MOS Capacitances**

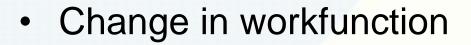

Difference in workfunction between the metal (polysilicon) semiconductors influences on the threshold voltage  $V_T$