|

Imran Muhammad |

|

Research Profile |

|

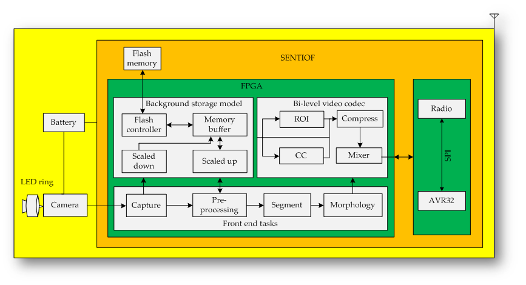

This is the core research area that I am involved in STC research center, Mid Sweden University, Sweden. STC has around 80 researchers and is headed by Prof. Mattias O’Nils. In this work, aim is to explore architectures for wireless smart cameras which are characterized by low energy, low latency and re-configurability. To achieve this aim, we look into design methods and implementation techniques that targets these characteristics with respect to both software (microprocessor) and hardware (FPGA) platforms. The research has strong relevance to industrial use-cases, specifically · Machine vision and IoT applications · Surveillance applications The activities related to this research work include, (1) Surveillance for Safety Applications:: Thermal-Visual Based Smart Camera System In this system, the aim is to develop IR-Visual Based Smart Camera System. The project aims at development of autonomous smart camera based monitoring and notifying system which will help reduce the accidents. For more details click [ link ] [ funding ]. The project can be motivated by one of the unfortunate events, such as this [ link ]. (2) ASIS:: In-Sensor Processing for Autonomous Industrial Wireless Sensor Networks [ link ] This project aims at exploration of methods and design space space exploration for in-node processing in the context of industrial wireless sensor networks. The study will provide guidelines on how to perform complex computations locally on the node for real-time industrial wireless sensor systems which has both low eneryg and low latency requirement. (3) Taxonomy formulation and complexity model for smart camera systems, Available online. Here, we present an approach for characterizing the embedded smart cameras by functions they performed. In addition to this, an abstract model for comparison of different smart camera systems is presented. (4) Intelligence partitioning for smart camera on software, hardware and locality. Available online The wireless smart cameras are still at infancy stages, though a lot of researchers, both in academic and industry, are working on this emerging technology. To solve some of the challenges, we come up with a biological inspired approach that intelligence of the smart camera should be shared with matured technology of server/base station. Our investigation showed that front end pixel based tasks can be efficiently performed on FPGA, following this compressed data can be transmitted to server for further processing of high level tasks. However, challenge is to reduce amount of transmission data, for which we developed a novel bi-level image coding technique.

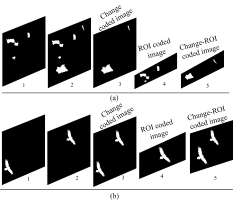

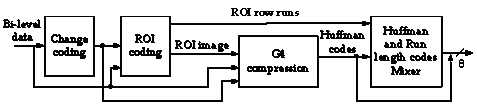

(5) Light weight image coding techniques An intelligent bi-level image coding method which has low design complexity, low processing energy and still reduce data in the order of magnitude. [ link ]

(6) Duty cycling for SRAM FPGA This work result in development of SRAM FPGA based wireless smart camera called SENTIOF-CAM which can effectively utilize duty cycling. This is in contrast to traditional thinking that SRAM FPGA cannot be used for duty cycling because of greater configuration time and high static power consumption. Details can be accessed online [ link ] [ link ] . See video below.

|

|

Low energy and re-configurable architecture for wireless smart camera |

|

muhammad.imran@miun.se |

|

SENTIOF-CAM, a low energy and re-configurable smart camera architecture and Hardware |

|

Bi-Level video codec architecture and sample images |

|

Almost everything — all external expectations, all pride, all fear of embarrassment or failure - these things just fall away in the face of death, leaving only what is truly important. |

|

Events |

|

Þ Ericsson grant for research [ link ] |

|

Þ Research visit (2015) to smart camera group, Alpen-Adria university, Klagenfurt. |

|

Þ PhD position in our group, march 15, 2015 deadline. |

|

Þ Sandeep will present Master thesis about HLS tools for accelarating development time on FPGA |

|

Þ Demo and paper presented in ICDSC 2014, Italy.

|

|

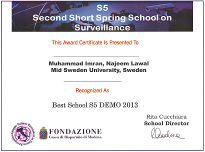

Þ Best Demo award at Spring surveillance school (2013), Modena, Italy

|

|

Þ Conference paper presented in 16 Euromicro DSD conference, 2013, Spain.

|

|

Þ A conference paper in Networked embedded systems (NESEA) conference, 2012, UK. |

|

|

|

|